Quick Generate

Create Your Own AI Model

Model Description by Creator

Warning.

The use of this LoRA is prohibited for illustrations where the generated results appear to be, or would be, underage.

Whether the generated illustration is R18 or not is completely irrelevant. It is prohibited even for all-ages content. "It is troublesome to judge whether it is OK or not one by one! It would be easier to ban it uniformly."

Even if the actual age is 495, if the generated result looks like a minor, it is not permitted.

In the unlikely event that I discover a violation of this rule, there is a "possibility*1" that I will take action as I deem appropriate, taking into account platform, maliciousness, etc.

The "possibility*1" here is not a common sense possibility. The "possibility*1" is within the scope defined at the end of this document.

As a general rule, I will deal with violations that I myself find according to "possibility*1". In the case of violations against the rules of each platform, please deal with it according to the rules provided by the platform provider, as it will be the platform's problem.

Important things to prevent problems

Only for the above violations, even if you guys find them, please avoid pointing them out directly. It may cause trouble with users.

What? Did you get into trouble with the violator by pointing it out directly? I don't know, solve it by yourself. Even if you ask me for advice, I will throw your message in the trash.

Purpose

This LoRA is designed to generate illustrations dressed by mature women and to enjoy the gap between them! No other use is envisioned! Well, even a good-looking gentlemen will work. Maybe.

How to use

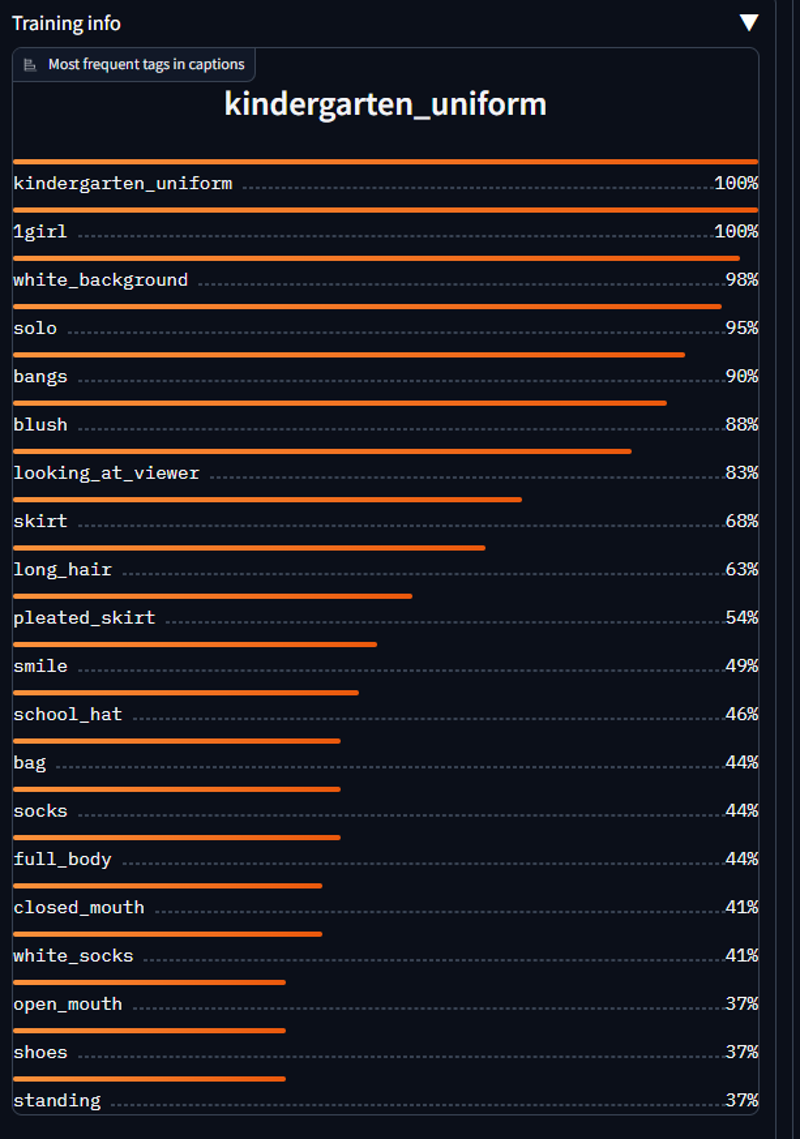

Trigger words: kindergarten_uniform

For "big breasts~huge breasts" adult women: 1.2~1.3 is recommended.

1x is recommended for flat chested adult females.

Optional word: school_hat, bag, school bag, [color]_skirt OR [color] skirt, pleated_skirt

Negative (Oprional): animal ears

Deprecated in most cases: white_background

possibility*1

The definition of "possibility*1" is "n" within the following range.

1 / R3 ≤ n ≤ 1

Note that R3 refers to the value stored in register 3, not R*3.

Theoretical machine executing pseudo-assembly code: it has infinite computation speed and registers (R1~R8) capable of storing infinite bits.

Well, it doesn't matter if it is finite; a register that can store G(64) bits should be sufficient.

The specifications of each instruction are as follows.

Instruction: LOAD Rn, x

Summary: Loads the value x into the register Rn.

Instruction: LOAD Rn, Rm

Summary: Loads the value of register Rm into register Rn.

Instruction: CMP Rn, x

Summary: Compares the value of register Rn with the value x.

Instruction: JZ label

Summary: If the results of the previous CMP instructions are equal, jump to label label.

Instruction: JMP label

Summary: Jump to label label.

Instruction: DEC Rn

Summary: Rn <- Rn - 1

Instruction: POW Rn, Rm

Summary: Rn <- Rn ^ Rm

Code

#############################

START

LOAD R1, 2

LOAD R2, 65536

LOAD R3, R1

LABEL loop

CMP R2, 0

JZ end

DEC R2

POW R3, R1

JMP loop

LABEL end

END

#############################

Images Generated With This Model

Create Your Own AI Model

Create Your Own AI Model

Create Your Own AI Model

Similar Models

Create Your Own AI Model

Create Your Own AI Model